DRAM(Dynamic Random Access Memory)是現代電腦系統中最基礎的記憶體技術,其核心原理是利用電容器儲存電荷來記錄資料。DRAM的基本結構非常簡單,由無數個記憶單元組成網格狀陣列。每個記憶單元包含兩個基本元件:一個電晶體和一個電容器,這就是所謂的1T1C結構。當電容器儲存電荷時,表示"1";無電荷時則表示"0"。

https://www.youtube.com/watch?v=I-9XWtdW_Co

DRAM的讀取操作是通過感測放大器來完成的。當進行讀取時,位元線會檢測電容器的電荷狀態,這個過程會導致原有電荷的釋放,因此讀取操作本質上是破壞性的。為了保持資料的完整性,系統必須在讀取後立即執行重寫操作。由於電容器存在漏電流,儲存的電荷會隨時間逐漸減少,這就是DRAM"Dynamic"特性的由來。為了防止資料丟失,系統需要定期對所有記憶單元進行重整操作,通常每64毫秒進行一次。重整過程會消耗能量並佔用部分記憶體頻寬。DRAM的存取速度受限於電容器的充放電時間,這導致其存取延遲相對較高。同時,頻繁的充放電和重整操作也造成了較高的功耗。隨著製程技術的進步,電容器的尺寸不斷縮小,但這也帶來了電容值降低和保持時間縮短的問題。

現代DRAM技術已發展出多種專業變體,針對特定應用場景。目前市面上主要的DRAM包括DDR5、LPDDR5X、GDDR6X和HBM3E,DDR5作為主流標準,採用DIMM封裝提供最大記憶體容量,廣泛應用於一般電腦和伺服器系統。通過R-DIMM可以實現更大容量,但會因為封裝複雜性和額外的暫存器而提高成本。

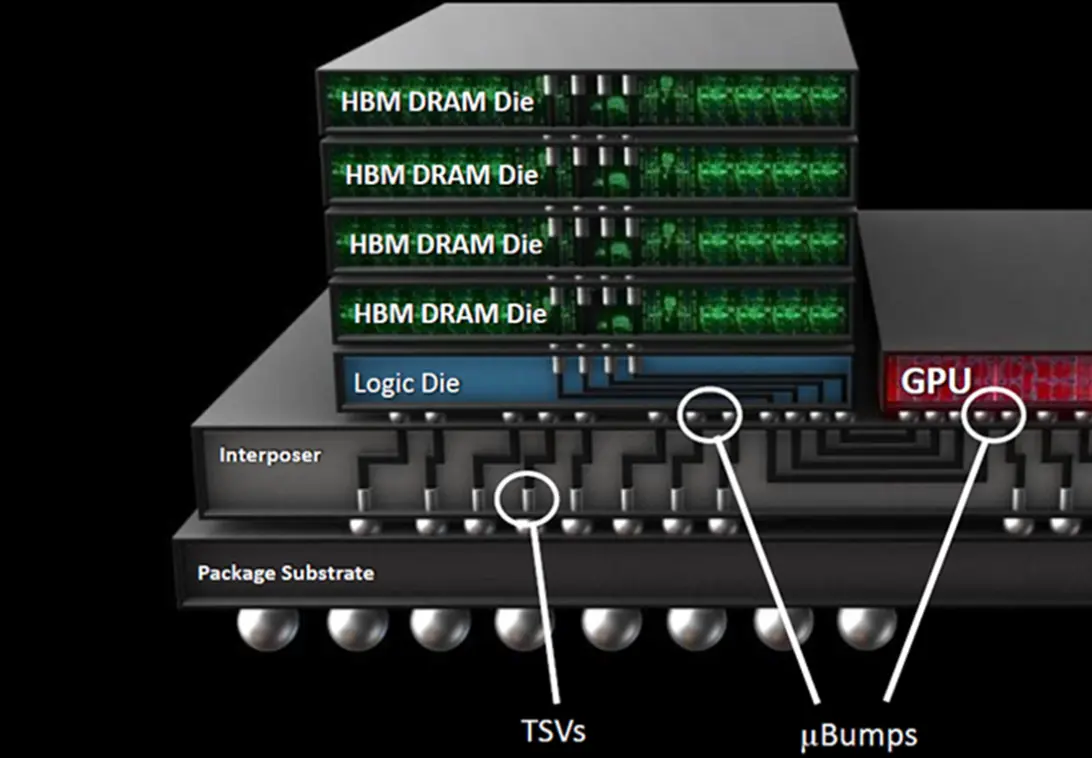

HBM3E代表了DRAM技術的巔峰,其特色在於精密的垂直堆疊結構,通常包含8到12片DRAM晶片,採用了矽穿孔(TSV)技術,每片都需要完美對齊並通過TSV相互連接,任何細微的偏差都可能導致整個結構失效。想像一棟大樓,TSV像是貫穿每一層的高速電梯,確保各層之間的快速通訊。在HBM3E中需要容納超過1,200條訊號線,遠超傳統記憶體的連接數量。這種高度複雜的製程使得每片HBM DRAM晶片的面積達到傳統DDR晶片的兩倍,同時也對晶片的電氣性能和散熱能力有更嚴格的要求。

當前市場上的主要HBM供應商面臨著不同的技術挑戰。三星由於使用較舊的製程技術(1α節點)且存在設計問題,導致良率表現不佳。SK海力士憑藉其創新的MR-MUF封裝技術,成功實現了穩定的HBM3E生產。美光雖然擁有可行的技術方案,但仍需要時間來提升產能。此外HBM製造成本居高不下,每GB成本遠高於DDR5的三倍,但在追求高性能AI運算的需求下,廠商不得不採用這種昂貴的解決方案。現況更令人擔憂的是,HBM技術的複雜度持續提升,堆疊層數不斷增加,從成本結構來看,NVIDIA H100的HBM成本已佔總製造成本的一半以上,到了新一代Blackwell架構甚至提高到60%以上。

目前HBM4的研發已在進行中,但不改DRAM技術發展正面臨瓶頸的事實。目前計算能力與記憶體技術的發展差距不斷擴大,產業急需在DRAM領域尋求突破。由於AI產業有數千億美元的資本支出,這給予產業強大的動力去推動新的解決方案。長期而言有各種五花八門且複雜的方案,但本文重點在於探討短期能見度最高的方案—3D DRAM

What is 3D DRAM?

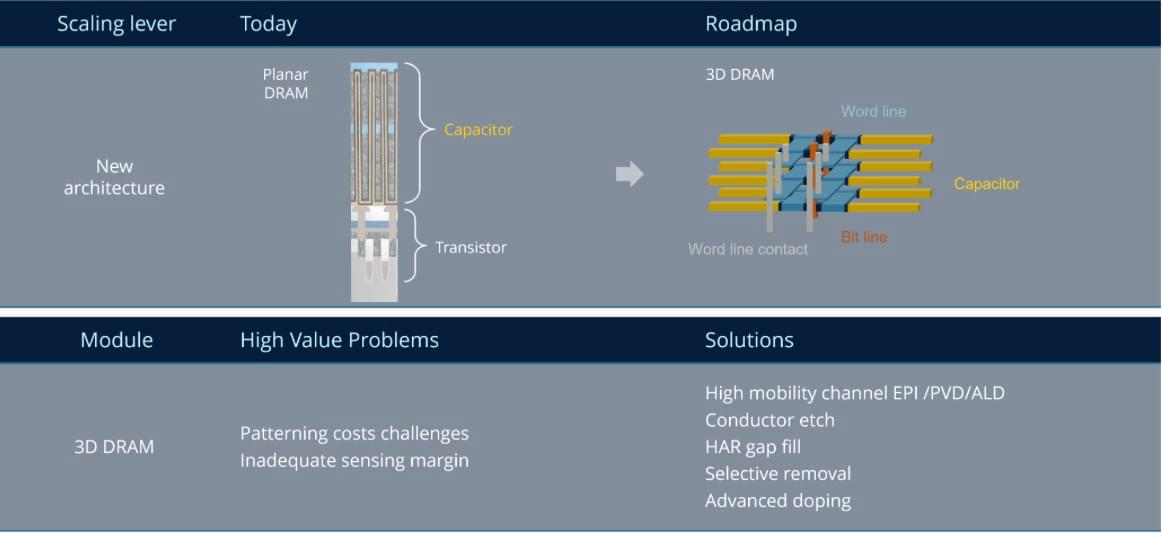

3D DRAM指的是在垂直方向儲存位元的架構,將電容器旋轉並垂直堆疊。密度提升不是通過縮小實現的,而是通過在裝置中堆疊更多層來達成。事實上NAND Flash記憶體大約十年前就開始了革命性的轉變,從平面結構改為垂直堆疊設計。這種設計從最初商用產品的32層,已經發展到現在快要達到1000層的程度。

雖然DRAM的基本結構比NAND的設計複雜,但其製造理念類似。製程首先會堆疊多層成本較低的基礎材料,這些材料本身並沒有特定的功能結構。接著使用精密的蝕刻技術從上往下進行處理,配合特殊的化學製程,在這些材料層中同時製作出大量的電晶體和電容器,形成完整的記憶體結構。3D DRAM沒有激進的創新,唯一的重大改變在於製造技術,而且通常能與記憶體內運算(CIM)架構相容,換句話說,是失敗風險最低的選項。

3D DRAM 實際進展

三星在2024年的Memcon大會上首次公開了他們的3D DRAM發展計劃,稱之為VS-DRAM(Vertically Stacked DRAM)。目前他們還在探索不同的技術路線,包括vertical wordline和vertical bitline兩種設計方案。雖然他們已經能夠製造出可以運作的實驗性產品,並完成了基本的電性測試,但這項技術還需要更多時間才能達到量產水準。

SK Hynix則在這場技術競賽中走得更快。在2024年的VLSI研討會上,他們展示了一款具有5層vertical bitline整合的新型DRAM,並且已經規劃在未來的0a製程節點(大約5年後)正式採用這項技術。他們選擇了vertical bitline的設計方案,因為這種設計能提供更好的sensing margin。而且,他們已經展示出一個完整的產品原型,成功地將memory array和peripheral circuitry透過hybrid bonding技術整合在一起。

https://www.trendforce.com/news/2024/06/24/news-sk-hynixs-5-layer-3d-dram-yield-reportedly-hits-56-1/

http://m.chinaaet.com/article/3000166964

記憶體產業正在為下一代3D DRAM技術做準備,雖然距離實際量產還需要一段時間,但AI的強勁需求將會加速研發時程。

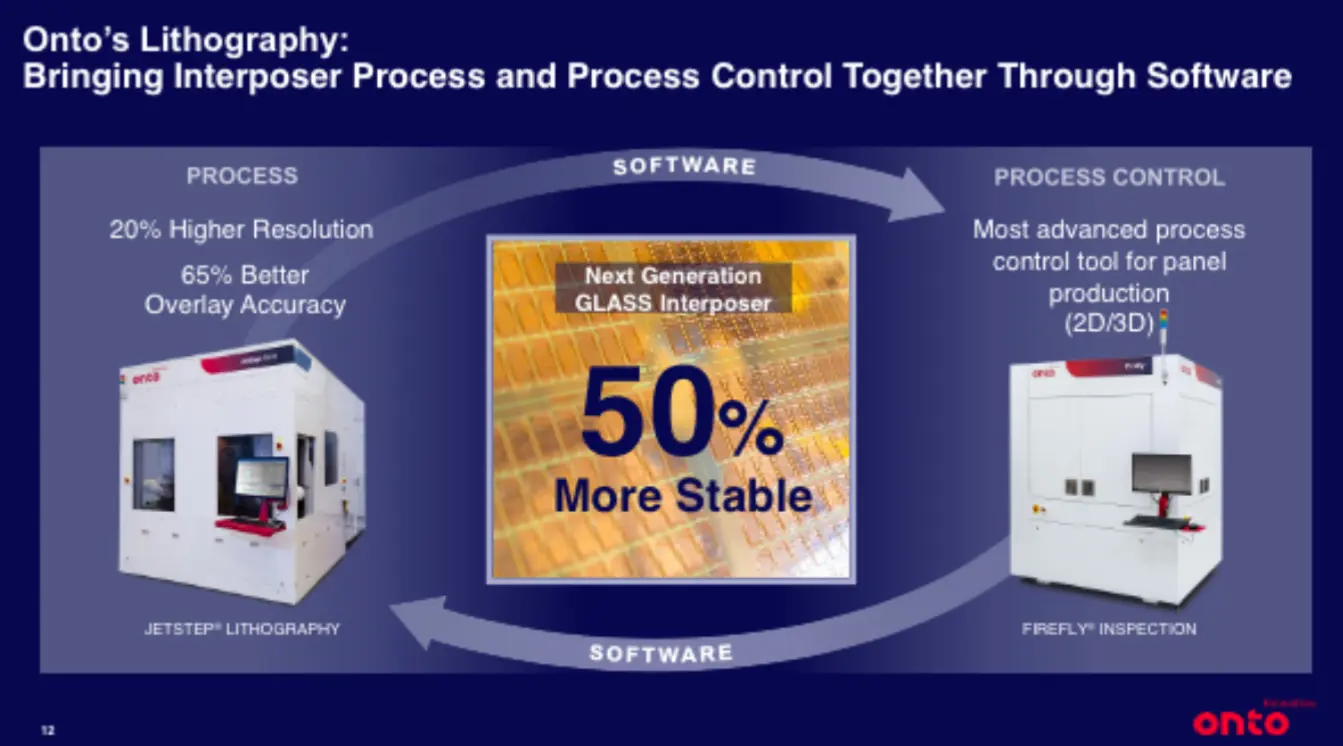

過去在NAND、DRAM和邏輯晶片的製造中,最重要的就是光刻技術,因為要做出更小的元件,就必須能夠在晶圓上印出更精細的圖案。發展3D DRAM意味從過去追求平面上的微縮,轉向垂直方向的堆疊,密度擴展是通過簡單地增加更多垂直層來實現,而記憶體單元保持相同大小。但新的挑戰出現了,比如要在材料中鑽出非常深且細的洞(深度是寬度的100倍),或是要在看不到的表面上,精確地橫向沉積只有1奈米厚的材料層。因應新的製程挑戰,需要全新的設備和技術來解決 。 (待續…)

諗緊今晚入

諗緊今晚入

好撚後悔

好撚後悔