Samsung Galaxy 討論區 (187) A33/A53/A73 幾時有價幾時上市?

stepmic

1001 回覆

7 Like

1 Dislike

第 1 頁第 2 頁第 3 頁第 4 頁第 5 頁第 6 頁第 7 頁第 8 頁第 9 頁第 10 頁第 11 頁第 12 頁第 13 頁第 14 頁第 15 頁第 16 頁第 17 頁第 18 頁第 19 頁第 20 頁第 21 頁第 22 頁第 23 頁第 24 頁第 25 頁第 26 頁第 27 頁第 28 頁第 29 頁第 30 頁第 31 頁第 32 頁第 33 頁第 34 頁第 35 頁第 36 頁第 37 頁第 38 頁第 39 頁第 40 頁第 41 頁

响大6個生態,完全唔會考慮an機

同樣4nm但轉咗TSM降左2-3度, 8G1 plus 咪同8G1一樣?如果大家一樣spec。

心水清果啲就會知

邊部機係大陸機啲發佈會屌打得最多就邊部最好

邊部機係大陸機啲發佈會屌打得最多就邊部最好

因為佢冇A15+IOS融合

S8G1相比A15又食電, 佢又調教得差, 所以咪要係充電入手

S8G1相比A15又食電, 佢又調教得差, 所以咪要係充電入手

幾年前去鄰國探親

真係有親戚拎啲類似嘅表走嚟笑鳩我部iPhone冇佢部紅米咁好

真係有親戚拎啲類似嘅表走嚟笑鳩我部iPhone冇佢部紅米咁好

D9000

首先我們要通讀發哥的論文,他說N4的良率非常成熟,不存在體質上的巨大差異,這是發哥的論文告訴我們的,而且從實際出發,由n5進行微縮得到的n4本來就應該是成熟工藝,畢竟庫都是通用的,二者本質上就是一代節點。

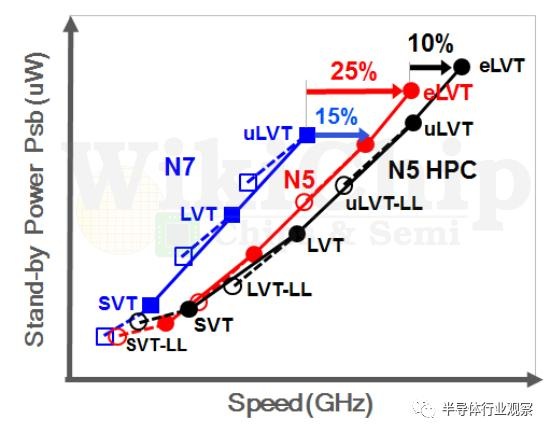

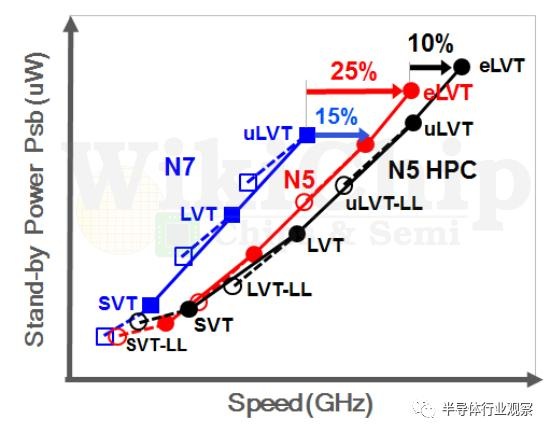

再回到論文的重點,發哥的整個cpu都使用了tsmc的 N4性能庫,並且X2內核為了滿足預設的頻率目標使用了部分ulvt,並儘可能的最少使用elvt單元,這裡需要引入一張圖,橘貓爪給我的,這張圖,我們可以清晰的明白待機功耗和頻率以及單元庫設計3者之間的關係。 基本上在N5這個節點為了達到更高的頻率,性能庫必須用低閾值電壓單元,頻率越高需要的電壓閾值單元就越低,但是這些單元越低,待機功耗就越高(leakage,半導體物理特性),就是這麼尷尬。

回到天璣9000,他的x2為了達到預設的3.4ghz頻率使用了ulvt和最少的elvt來實現,所以這很可能是發哥這次高頻功耗不太好看的一個原因之一,這也可能是導致用了性能庫,功耗卻沒跟4lpx的性能庫拉開的原因。 畢竟使用這兩種單元庫造成的leakage理論上是最高的。

再來看發哥的a710,論文上寫的是使用了低漏電的ulvt單元,也就是圖上的ULVT-LL單元,且避免使用LVT單元以保持頻率,可以看到空載降低了不少比起ulvt,但是頻率也下降了,因此降低了洩漏功率並將a710的可用範圍擴展到更低的電壓和頻率。 (發哥的論文都是寶,到底出了什麼問題,懂的人大概都看得見)

由此我們也可以得出為什麼市面上的四台評測工程機呈現出來比較矛盾的結果,首先點名jkw,在這種高空載的情況下,做出那種不現實的dou吊打,你不嫌丟人麼? 知道這幾台工程機的空載有多離譜麼? 反而愛否和草這倆人的更合理一些,畢竟全部都是性能庫,空載擺在那,為了邏輯自洽我能理解,但是吃相是否太難看了。

首先我們要通讀發哥的論文,他說N4的良率非常成熟,不存在體質上的巨大差異,這是發哥的論文告訴我們的,而且從實際出發,由n5進行微縮得到的n4本來就應該是成熟工藝,畢竟庫都是通用的,二者本質上就是一代節點。

再回到論文的重點,發哥的整個cpu都使用了tsmc的 N4性能庫,並且X2內核為了滿足預設的頻率目標使用了部分ulvt,並儘可能的最少使用elvt單元,這裡需要引入一張圖,橘貓爪給我的,這張圖,我們可以清晰的明白待機功耗和頻率以及單元庫設計3者之間的關係。 基本上在N5這個節點為了達到更高的頻率,性能庫必須用低閾值電壓單元,頻率越高需要的電壓閾值單元就越低,但是這些單元越低,待機功耗就越高(leakage,半導體物理特性),就是這麼尷尬。

回到天璣9000,他的x2為了達到預設的3.4ghz頻率使用了ulvt和最少的elvt來實現,所以這很可能是發哥這次高頻功耗不太好看的一個原因之一,這也可能是導致用了性能庫,功耗卻沒跟4lpx的性能庫拉開的原因。 畢竟使用這兩種單元庫造成的leakage理論上是最高的。

再來看發哥的a710,論文上寫的是使用了低漏電的ulvt單元,也就是圖上的ULVT-LL單元,且避免使用LVT單元以保持頻率,可以看到空載降低了不少比起ulvt,但是頻率也下降了,因此降低了洩漏功率並將a710的可用範圍擴展到更低的電壓和頻率。 (發哥的論文都是寶,到底出了什麼問題,懂的人大概都看得見)

由此我們也可以得出為什麼市面上的四台評測工程機呈現出來比較矛盾的結果,首先點名jkw,在這種高空載的情況下,做出那種不現實的dou吊打,你不嫌丟人麼? 知道這幾台工程機的空載有多離譜麼? 反而愛否和草這倆人的更合理一些,畢竟全部都是性能庫,空載擺在那,為了邏輯自洽我能理解,但是吃相是否太難看了。

而家samsung同TSM製程分別主要是良率嗎?如果雙方做同一粒最好既8 gen1 又相差幾遠?

原來11巴已經全家轉哂三星

原來11巴已經全家轉哂三星估計係:

快速:10-15W (PD non PPS, Quick Charge 2.0)

超快速:25W (PD PPS 25W)

超快速 2.0:45W (PD PPS 45W)

快速:10-15W (PD non PPS, Quick Charge 2.0)

超快速:25W (PD PPS 25W)

超快速 2.0:45W (PD PPS 45W)

主要係良率同漏電率

良率其實唔怕, 因為出得街一般都冇問題, 良率應該只影響貨量同SAMSUNG自己生產成本

良率其實唔怕, 因為出得街一般都冇問題, 良率應該只影響貨量同SAMSUNG自己生產成本

佢昨天已完成該計劃

轉哂s21fe?

未完全完成, 我記錯

11巴 - S22U, X1 III

父親 - 等S21FE黑色返貨

母親 - S21FE 紫色

11巴 - S22U, X1 III

父親 - 等S21FE黑色返貨

母親 - S21FE 紫色

VoLTE真係好浪費電但關唔到

VoLTE唔食電, 最食電係5G

但開左真係耗電多左

加左,係唔係咁?

轉會轉得好快手

冇試過關VOLTE

VOLTE只係用4G通話, 平時應該唔會點用電

VOLTE只係用4G通話, 平時應該唔會點用電

多D人用其實好事黎, 市面太多iPhone了, 搞到好多自大井底盲撚